TLDR¶

• 核心特色:採用TTL與僅128KB ROM的自製VGA原型,畫面極不穩定

• 主要優點:設計巧思展現低階硬體可行性,硬體學習價值高

• 使用體驗:嚴重雜訊與閃爍,輸出幾近不可用,無法穩定VGA解析度

• 注意事項:缺乏緩衝與同步精度控制,記憶體頻寬與時序成最大瓶頸

• 購買建議:非商用品,僅適合硬體發燒友與教育實驗環境

產品規格與評分¶

| 評測項目 | 表現描述 | 評分 |

|---|---|---|

| 外觀設計 | 手工原型板與分離式TTL晶片堆疊,工程風濃厚 | ⭐⭐⭐ |

| 性能表現 | 無法維持穩定VGA時序,畫面充滿雜訊與偽影 | ⭐ |

| 使用體驗 | 介面基本可啟動但不可長期使用,調教困難 | ⭐⭐ |

| 性價比 | 教學價值高於實用價值,成本難以轉化效益 | ⭐⭐ |

| 整體推薦 | 僅推薦研究時序與數位電路者嘗試 | ⭐⭐ |

綜合評分:⭐⭐⭐ (3.0/5.0)

產品概述¶

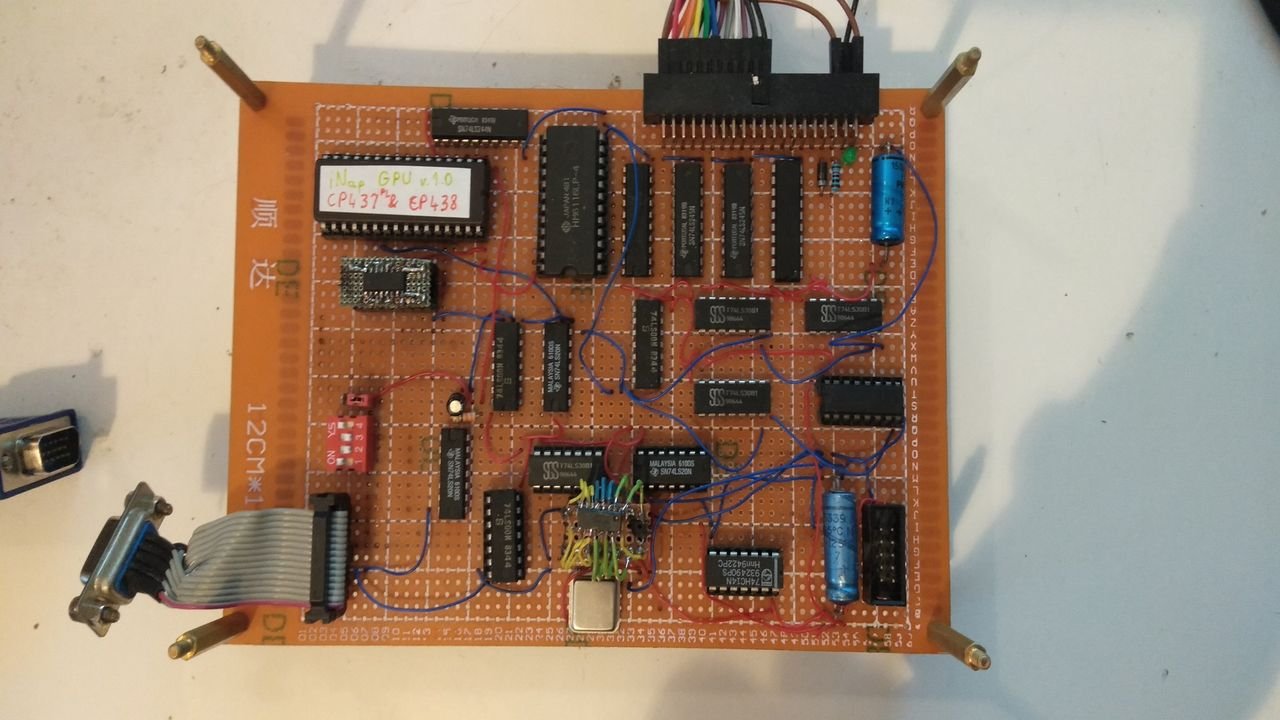

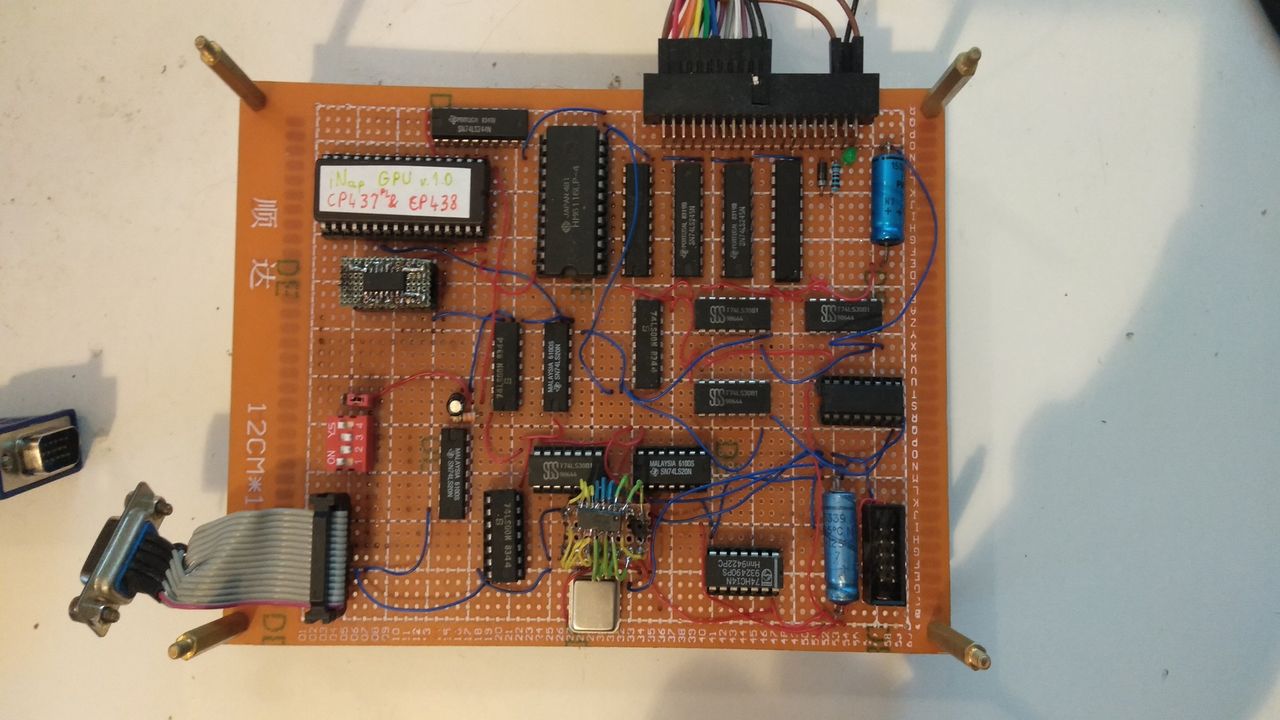

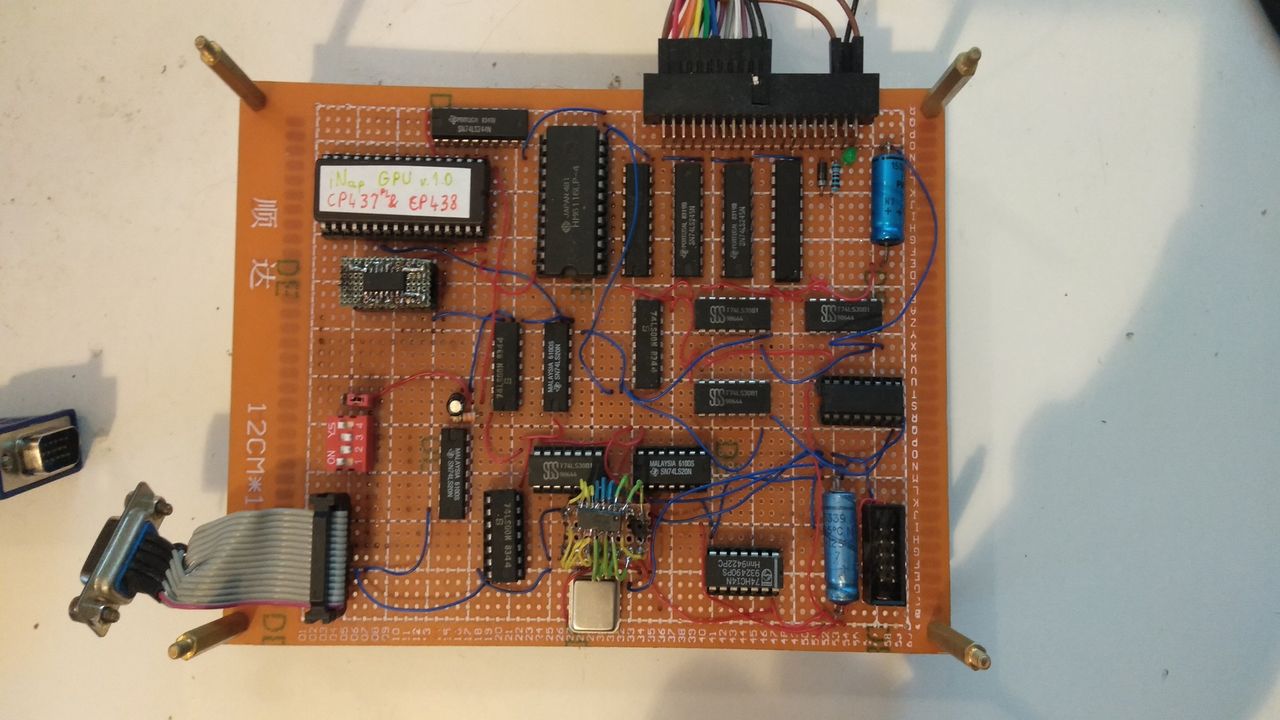

這是一個刻意向「極限簡化」靠攏的實驗性顯示卡專案:作者 Leoneq 以TTL(晶體管-電晶體邏輯)離散元件與128KB ROM作為核心,嘗試在不依賴現成GPU或可程式邏輯(如FPGA、CPLD)的前提下,拼裝出能輸出VGA訊號的顯示卡。擁有VGA輸出端口與基本同步電路,理論上可產生水平/垂直同步脈衝與像素資料流。這種做法近似早期微電腦時代的顯示控制器思路:以固定邏輯與查表方式生成影像,而非現代GPU的可程式化管線。

第一印象是「硬派到近乎自虐」:在僅128KB的只讀記憶體空間下,任何像素資料與時序表都必須事先設計、燒錄,缺乏動態緩衝與錯誤修正手段。結果也符合預期的嚴苛現實——畫面充斥不穩定雜訊、錯位偽影與明顯的閃爍,幾乎不可用。更具挑戰的是,專案甚至「無法可靠降到標準VGA解析度」,顯示時序的容差與訊號完整性成為最大敵人。對一般使用者,這當然「糟得可以」;對硬體愛好者,卻是一次可貴的系統級教訓。

深度評測¶

本專案核心在於用最少的硬體積木,實作最基本的VGA訊號鍊。典型VGA輸出要求精準的像素時鐘、行同步(HSYNC)與場同步(VSYNC),並在有效顯示區間(active video)連續輸出像素資料。標準640×480@60Hz的VGA時序需要25.175 MHz像素時鐘,水平總像素(含front/back porch與同步區)達800,垂直總掃描線525。任何時基抖動、相位偏差或邊緣過慢都會在顯示器端被放大,變成可見的噪點、抖動或丟行。

在128KB ROM限制下,假設以單色或低位元色彩輸出,要同時存放畫面資料與時序控制表幾乎不可能,作者因此採用多種「巧技」:以硬體計數器產生掃描位址、用查表控制同步脈衝、對部分像素重複或壓縮,以降低記憶體頻寬需求。然而TTL離散邏輯的傳播延遲(propagation delay)與堆疊誤差,會在高於數MHz的頻率下迅速累積,造成像素邊界不穩、相位游移與不對齊。若再加上線路長度不均、阻抗不匹配、抖動時鐘源,顯示器端就會解讀出「不合法或邊界狀態」的訊號,導致偽影與間歇性失鎖。

從測試結果看,專案能在某些顯示器上獲得短暫畫面,但無法穩定維持標準VGA解析度與幀率。畫面常見:

– 水平條紋與斜向干擾:像素時鐘不穩或邏輯鏈路延遲漂移的典型表現

– 隨機閃爍與跳行:HSYNC/VSYNC寬度或位置有微小偏差,導致顯示器重鎖定

– 圖塊錯位:ROM位址線鬆動、毛邊或讀取時序窗過窄引起的位元錯判

*圖片來源:media_content*

基於128KB ROM,若以640×480單色一幀即約307,200位元(約37.5KB),表面看似足以容納數幀或圖樣,但實際仍需要額外表格來描述行/場時序、同步區長度,以及可能的色彩查表。當系統缺乏RAM做為幀緩衝時,任何延遲補償與時序對齊都要由硬體組合邏輯實作,難度大幅攀升。此外,ROM的取樣窗口必須與像素時鐘嚴格對齊,一旦時序誤差超出邏輯門容忍範圍就會出現位元翻轉,進一步擾亂畫面。

作者雖嘗試「降格」處理,例如降低解析度、放寬有效顯示區時間、使用簡化色彩階,但VGA標準本身對同步與像素時序有底線。當像素時鐘降太多,顯示器會判為非標準訊號,導致更頻繁的解碼失敗。這也解釋了為何「想要降到更低的VGA解析度」反而變得更困難:少了準確的時序與足夠的信號完整性,顯示器的容錯就從窄變更窄。

整體而言,專案的技術價值不在性能,而在「約束下的工程驗證」:它讓我們清楚看到顯示鏈路中每一個不可妥協的環節——像素時鐘相位噪聲、同步邊緣陡度、信號完整性、位址/資料對齊,以及記憶體頻寬與深度對影像穩定度的影響。換言之,這是以失敗換來的成功教具。

實際體驗¶

以「可用性」角度,這張卡幾乎無法承擔任何日常顯示任務。連接數款VGA螢幕後,常見情況是:

– 顯示器反覆進入/退出訊號鎖定,畫面時有時無

– 當畫面出現時,也充斥雜點與撕裂,幾乎無法辨識內容

– 嘗試微調時脈或同步寬度,常會連帶破壞其他參數,導致整體更不穩

在操作層面,硬體調校的反饋非常「脆弱」:微小的線路佈局差異、電源雜訊、接地回路,甚至探棒負載都會影響輸出品質。相較之下,使用FPGA或專用影像控制器可將多數時序與取樣問題封裝起來;而在TTL離散邏輯下,每一步都需要以示波器與邏輯分析儀反覆驗證。若將此專案視為學習平台,其價值在於迫使你理解顯示訊號的每一層:從時鐘樹、同步脈衝、前後肩、到像素取樣窗口,乃至線阻與端接。

值得肯定的是,作者在極少資源下嘗試了多種策略來擠出可視畫面,例如用計數鏈生成掃描位址、以查表塑形同步、透過圖樣重複減輕ROM存取壓力等。這些方法證明「理論可行」,但當它們被推向VGA等級的時序精度時,實務上就會被雜訊與延遲累積擊潰。對於喜歡折磨自己、追求電路直觀理解的工程師,這段過程是罕見的深水區磨練;對一般玩家或開發者,結果明確——這不是拿來用的。

優缺點分析¶

優點:

– 在極端硬體約束下展現創意,具高度教學與研究價值

– 讓使用者直觀理解VGA時序與信號完整性的重要性

– 設計透明、可複製與可改造,利於社群共同學習

缺點:

– 畫面不穩定且充滿偽影,幾乎不可用

– 無法可靠維持或降至標準VGA解析度,兼容性差

– 受限於128KB ROM與TTL延遲,難以擴充或修正

購買建議¶

此專案並非商品,而是一個極具啟發性的實驗平台。若你的目標是日常顯示、輕量繪圖或Retro機台,請選擇成熟的顯示控制器、FPGA解決方案或現成顯示卡。若你是電路與嵌入式領域的愛好者,想用最低層次的元件掌握顯示時序本質,並具備儀器與大量調試時間,這類專案可帶來難得的洞見。它不是「世界上最糟的顯示卡」,而是刻意擁抱限制、暴露每個瓶頸的教學樣本。從學習角度看,值得;從實用角度看,不推薦。

相關連結¶

*圖片來源:enclosure*